# Analysis and Design of Low Voltage Low Power Dynamic Comparator with Reduced Delay and Power

Dinabandhu nath Mandal<sup>1</sup>, Niladri Prasad Mohapatra<sup>1</sup>, Rajendra Prasad<sup>3</sup>, Ambika Singh<sup>1</sup>

<sup>1</sup>Research Scholar (M.Tech), Department of Electronics, KIIT University, Bhubaneswar, India

<sup>1</sup>Assistant Professor, Department of Electronics, KIIT University, Bhubaneswar, India

Email-mandaldinbandhu@gmail.com

Abstract— High speed devices such as ADC, operational amplifier are of great importance and for this high speed application a major thrust is given towards low power methodologies. Reduction of power consumption in these device can be achieved by moving towards smaller feature size processes. Now ADC requires lesser power dissipation, low noise, better slew rate ,high speed etc. Dynamic comparator are being used in today's A/D converters extensively because these comparator are high speed ,consumes lesser power dissipation ,having zero static power consumption and provide full-swing digital level output voltage in shorter time duration. Back to back inverter in these dynamic comparator provides positive feedback mechanism which convert a smaller voltage difference in full scale digital level output. A pre-amplifier based comparator can amplify a small input voltage difference to a large enough voltage to overcome the latch offset voltage and also can reduce the kickback noise. However the pre-amplifier based comparator suffer large static power consumption as well as from the reduced intrinsic gain with the reduction of the drain to source resistance due to continuous technology scaling. In this paper a delay analysis has been presented for different dynamic comparators and finally a proposed designed has been given where delay has been reduced 264Ps and average power dissipation has been reduced to 1.09μw.The above design has been simulated in 180nm technology with a supply voltage of 0.8v

**Keywords**— High speed analog-to-digital comparators(ADCs), Dynamic clocked comparator, low power analog design, Double-tail dynamic comparator, conventional dynamic comparator, preamplifier based comparators

#### INTRODUCTION

Comparator is a fundamental building block in analog-to-digital converter(ADCs). In design of ADCs, comparator of high speed, low power consumption are used. comparator in ultra deep sub micrometer (UDSM) technologies suffers from low supply voltage. hence design of high speed comparator is a challenge when the supply voltage is low[1]. Hence to achieve high speed in a given technology more transistor are required and more area and power is required. Technique such as supply boosting method[2],[3] a technique such as body driven transistor[4],[5] has been developed to meet the low voltage design. In addressing switching problems and input range two technique such as boosting and bootstrapping are used. In this paper the delay has been presented for various dynamic comparator architecture. Based on the double-tail architecture a new dynamic comparator has been presented where delay is comparatively reduce compared to the earlier design which doesn't require boosted voltage. By adding a few number of transistor the delay time at the latch has been comparatively reduce. As a result in the modified design the power is saved and can be used for high speed ADCs design.

## CLOCK REGENERATIVE COMPARATORS

Clock regenerative comparator are widely use in design of ADCs of high speed as these type of comparator makes fast decision due to the presence of feedback(positive) in the latch stage. There are many analysis which investigate the behavior of the comparator from many respect such as random decision error[10], offset voltage[8], [9], noise[7], kick-back noise[11]. The the above section the

239 <u>www.ijergs.org</u>

analysis of delay is presented, the delay of the conventional dynamic and conventional double-tail comparator are verified and based on the above proposed comparator will be presented

## I. CONVENTIONAL DYNAMIC COMPARATOR

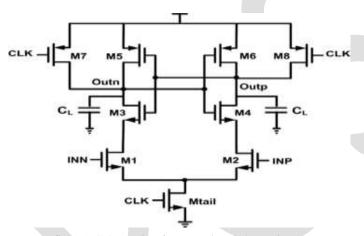

Conventional dynamic comparator is widely used dynamic comparator for the design of analog to digital comparator. It has rail-to-rail output swing ,high input impedance, zero static power consumption, the schematic of conventional dynamic comparator is shown in fig 1.1 and fig 1.2 shows the transient simulation of conventional dynamic comparator.

fig 1.1. Schematic of conventional dynamic comparator

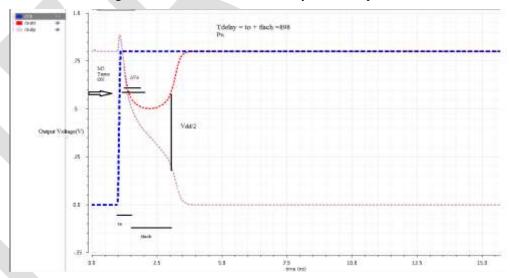

fig 1.2 :- Transient simulation of the conventional dynamic comparator for the voltage difference of 5 m V, V cm=0.7 and supply voltage of 0.8V

The delay of the above comparator consists of two delay  $t_0$  and  $t_{latch}$  where  $t_o$  discharging delay of the load capacitance  $C_L$  and  $t_{latch}$  is the latching delay of the cross coupled inverter and hence the total delay( $t_{delay}$ ) of the above comparator is given as

$$I_{\text{delay}} = I_0 + I_{\text{latch}}$$

$$= 2 \frac{C_L |V_{\text{thp}}|}{I_{\text{tail}}} + \frac{C_L}{g_{m,\text{eff}}} \cdot \ln \left( \frac{V_{\text{DD}}}{4 |V_{\text{thp}}| \Delta V_{\text{in}}} \sqrt{\frac{I_{\text{tail}}}{\beta_{1,2}}} \right). \tag{1}$$

240 <u>www.ijergs.org</u>

Where  $C_L$  is the load capacitance,  $|V_{thp}|$  is the threshold voltage of M2 transistor,  $g_{\textit{m.eff}}$  is the transconductance of the back-to-back inverter,  $V_{DD}$  is the supply voltage,  $I_{tail}$  is the current of the  $M_{tail}$  transistor.  $\beta_{1,2}$  is the current factor of the input transistor,  $\Delta$  Vin is the input voltage difference. According to equation (1) the delay of the above comparator depends directly to the load capacitance( $C_L$ ) and inversely to input difference voltage ( $\Delta$  Vin).

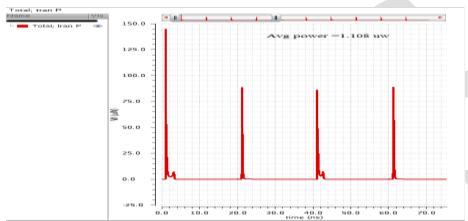

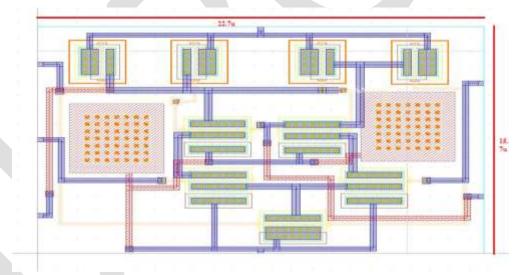

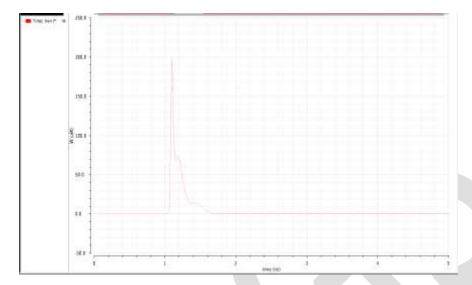

The main advantage of the above architecture are rail-to-rail swing at the output, better robustness against noise and mismatch, static consumption is zero. The power plot of the conventional dynamic comparator is shown in fig 1.3 and the layout of the above comparator is shown in fig 1.4

Fig 1.3 power plot of conventional dynamic comparator

Fig 4 Layout schematic of the conventional dynamic comparator

## II. CONVENTIONAL DOUBLE-TAIL DYNAMIC COMPARATOR

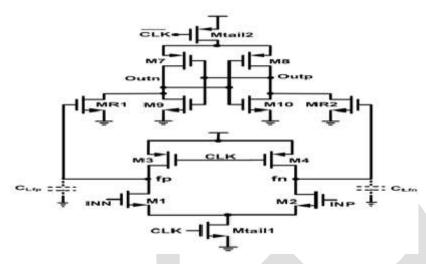

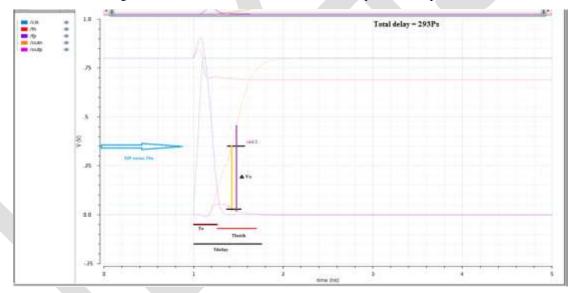

The schematic of double-tail dynamic comparator is shown in fig 1.5 as the above topology has large number of transistor and has less stacking and operation can be done at lower supply voltage compared to the earlier design of conventional dynamic comparator. As in these structure due to the presence of two M  $_{tail}$  transistor it provides large current at the latching stage and wider  $M_{tail2}$  requires for fast latching which is independent to V  $_{cm}$ (common mode voltage at input) and has small current at the input stage, required for low

offset[6]. The fig 1.6 shows the transient simulation of the conventional double-tail dynamic comparator for input voltage difference of  $\Delta V$ in=5mv ,  $V_{cm}$ =0.7v and  $V_{DD}$  = 0.8V

fig 1.5 Schematic of conventional double-tail dynamic comparator

Fig1.6 Transient simulation of the conventional double-tail dynamic comparator for input voltage difference of  $\Delta$ Vin=5mv ,V  $_{cm}$ =0.7v and  $V_{DD}$

The delay of the double-tail dynamic comparator comprises of two delay  $t_0$  and  $t_{latch}$ , which is similar to that of conventional dynamic comparator. Here  $t_0$  is the capacitive charging of the capacitance at the load C  $_{Lout}$ (at the outn and outp) until the transistor (M9/M10) are on, and hence the latch regeneration starts and  $t_0$  is determined. The total delay of the above comparator is given as

$$t_{\text{delay}} = t_0 + t_{\text{latch}} = 2 \frac{V_{\text{Thn}} C_{\text{Lout}}}{I_{\text{tail2}}} + \frac{C_{\text{Lout}}}{g_{m,\text{eff}}} \cdot \ln \left( \frac{V_{\text{DD}}/2}{\Delta V_0} \right)$$

$$= 2 \frac{V_{\text{Thn}} C_{\text{Lout}}}{I_{\text{tail2}}} + \frac{C_{\text{Lout}}}{g_{m,\text{eff}}}$$

$$\cdot \ln \left( \frac{V_{\text{DD}} \cdot I_{\text{tail2}}^2 \cdot C_{L,\text{fn(p)}}}{8 V_{\text{Thn}}^2 \cdot C_{L\text{out}} g_{\text{mR1,2}} g_{\text{m1,2}} \Delta V_{\text{in}}} \right).$$

where  $g_{mR1,2}$  is transconducatance of the transistor( $M_{R1}$  and  $M_{R2}$ ),  $I_{tail~2}$  is the current of  $M_{tail2}$  transistor,  $\Delta$  Vin is the voltage difference at the input,  $\Delta$  V<sub>0</sub> is the output voltage difference. The fig 8 and fig 1.7 below shows the power plot for calculating power and layout for determining area respectively of double tail dynamic comparator.

Fig 1.7-Power plot of double-tail dynamic comparator

Fig 1.8 - Layout of double tail dynamic comparator

## III PROPOSED DOUBLE TAIL DYNAMIC COMPARATOR

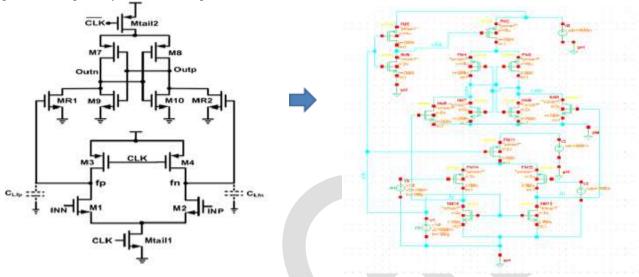

The schematic of proposed design is compared with double-tail dynamic comparator is shown in fig 1.9. In the proposed design the lower input state is replace by differential amplifier with PMOS load

Fig: 1.9 Schematic of proposed comparator(right) with double-tail dynamic comparator(left)

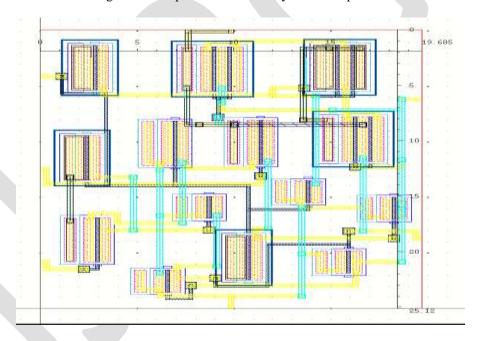

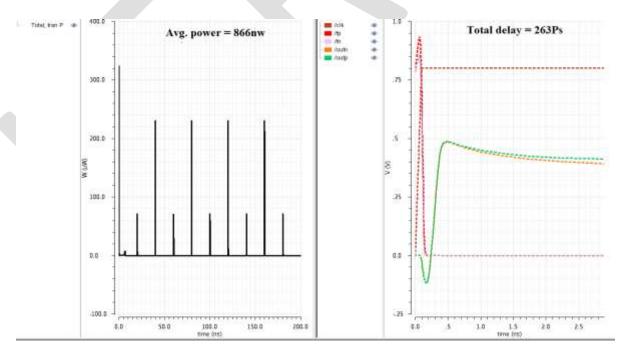

The delay of the proposed double-tail dynamic comparator is comparatively reduced in comparison to double-tail dynamic comparator. The power plot and Transient simulation of the proposed double-tail dynamic comparator for input voltage difference of  $\Delta Vin=5mv$ ,  $V_{cm}=0.7v$  and  $V_{DD}=0.8V$  is shown in fig 2.1 and fig 2.2 shows the layout of proposed double-tail dynamic comparator

Fig 2.1 :- Power plot and Transient simulation of the Modified double-tail dynamic comparator for input voltage difference of  $\Delta V$ in=5mv , $V_{cm}$ =0.7v and  $V_{dd}$  = 0.8V

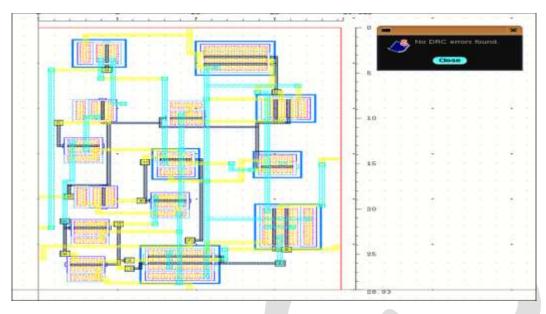

fig 2.2 Layout of proposed double-tail dynamic comparator in 180nm technology

# SIMULATION RESULT

The comparison table has been presented to compare the results of proposed comparator with conventional and double-tail dynamic comparators, the above circuit are simulated in a 180nm CMOS technology

| Comparator<br>Structure      | Conventional Dynamic Comparator | Double-tail<br>Dynamic<br>Comparator | Proposed<br>Double-tail<br>Dynamic<br>Comparator |

|------------------------------|---------------------------------|--------------------------------------|--------------------------------------------------|

| No of<br>Transistors<br>used | 9                               | 14                                   | 16                                               |

| Supply<br>Voltage (V)        | 0.8                             | 0.8                                  | 0.8                                              |

| Delay(Ps)                    | 898.2                           | 293                                  | 263                                              |

| Energy (FJ)                  | 1.108μ                          | 2.125 μ                              | 866 n                                            |

| Estimated<br>Area            | 22.7μ * 15.7μ                   | 28μ*13μ                              | 28.9μ*19.5μ                                      |

#### CONCLUSION

A new proposed double-tail comparator shows better performance as compared to conventional dynamic and double-tail dynamic comparator. As it is shown that the delay of the proposed design is 263 Ps which is comparatively lesser than the earlier also energy per conversion is reducing from  $1.108\mu$  in conventional dynamic to 866 ns in proposed double-tail. The proposed double-tail dynamic comparator can be used for the design of high speed ADCs as the delay is reduced and hence the operation will be faster. As in the proposed structure the number of transistor is more so the area of the design is more which is one of the disadvantage of the above comparator

### REFERENCES

- [1] B. Goll and H. Zimmermann, "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 56, no. 11, pp. 810–814, Nov. 2009

- [2] S. U. Ay, "A sub-1 volt 10-bit supply boosted SAR ADC design in standard CMOS," Int. J. Analog Integr. Circuits Signal Process., vol. 66, no. 2, pp. 213–221, Feb. 2011.

- [3] A. Mesgarani, M. N. Alam, F. Z. Nelson, and S. U. Ay, "Supply boosting technique for designing very low-voltage mixed-signal circuits in standard CMOS," in Proc. IEEE Int. Midwest Symp. Circuits Syst. Dig. Tech. Papers, Aug. 2010, pp. 893–896.

- [4] B. J. Blalock, "Body-driving as a Low-Voltage Analog DesignTechnique for CMOS technology," in Proc.IEEESouthwest Symp. Mixed-Signal Design, Feb. 2000, pp. 113–118.

- [5] M. Maymandi-Nejad and M. Sachdev, "1-bit quantiser with rail to rail input range for sub-1V modulators," IEEE Electron. Lett., vol. 39, no. 12, pp. 894–895, Jan. 2003

- [6] B. Murmann et al., "Impact of scaling on analog performance and associated modeling needs," IEEE Trans. Electron Devices, vol. 53, no. 9, pp. 2160-2167, Sep. 2006

- [7] R. Jacob Baker, Harry W. Li, David E. Boyce, "CMOS- Circuit Design, Layout, And Simulation", IEEE Press Series on Microelectronic Systems, IEEE Press, Prentice Hall of India Private Limited, Eastern Economy Edition, 2002

- [8] Meena Panchore, R.S. Gamad, "Low Power High Speed CMOS Comparator Design Using .18µm Technology", International Journal of Electronic Engineering Research, Vol.2, No.1, pp.71-77, 2010

- [9] M. van Elzakker, A.J.M. van Tuijl, P.F.J. Geraedts, D. Schinkel, E.A.M. Klumperink and B. Nauta, "A 1.9W 4.4fJ/Conversion-step 10b 1MS/s Charge-Redistribution ADC," ISSCC Dig. Tech. Papers, pp. 244–245, February 2008

- [10] Heungjun Jeon and Yong-Bin Kim, "A Novel Low-Power, Low-Offset and High-Speed CMOS Dynamic Latched Comparator", IEEE, 2010

- [11] Behzad. Razavi, "Design of Analog CMOS Integrated Circuits", New York McGraw-Hill, 2001

- [12] Dinabandhu Nath Mandal , Sanjay Kumar "High Speed Comparators for Analog-To-Digita comparatorl" IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331, Volume 9, Issue 2 Ver. III (Mar Apr. 2014), PP 5661